September-October 2023, Volume 3(05), 17-20.

# **Scan Chain Dependent Approaching Technique towards Fault Recovery**

# Ramakrishna Reddy Kareti<sup>1</sup>, Rajesh Nandalike<sup>2</sup>

<sup>1,2</sup> Department of Electronics and Communication Engineering, JAIN College of Engineering, Karnataka, India.

Article Type: Research

OPENACCESS

Article Citation:

Ramakrishna Reddy Kareti<sup>1</sup>, Rajesh

Nandalike<sup>2</sup> "Scan Chain Dependent

Approaching Technique towards Fault

Recovery", "International Journal of Recent

Trends In Multidisciplinary Research",

September-October 2023, Volume 3(05), 17-

©2027 he Author(s), This is an open access articled is tributed under the terms of the Creative Common Attribution. Leene, which permits unrestricted use, distribution, and reproduction in a common and acceptance of the common acceptance of the c

**Abstract:** Ongoing uses of all implanted framework will get disappointment because of numerous deficiencies happening in the framework. This issue ought to be identified and adjusted at the same time while running the framework. By and by we utilize an output chain based Triple particular overt repetitiveness (TMR) move toward strategy. It is pricey and requires multiple times more equipment assets. This paper investigates the use of decreased accuracy overt repetitiveness (RPR) to the issue, the measurement used to assess the viability of RPR is the piece blunder rate (BER) accomplished by the FPGA. RPR is applied to a genuine FPGA-based framework and is approved with broad shortcoming infusion tests. These technique can be accomplished by utilizing diminished check chain based various issue mistake recuperation (RSCMFER) strategy

**Key Word:** Continue Onward Mistake Recuperation, FIR channel, Triple Particular Overt repetitiveness (TMR) FPGA, Shortcoming discovery

#### 1. Introduction

A conventional TMR framework comprising of three repetitive modules and an elector at the modules yields has a few weaknesses that ought to be addressed to be utilized in wellbeing basic applications. A significant weakness of the conventional TMR is its powerlessness to adapt to TMR failures.TMR disappointment alludes to a disappointment in a TMR framework brought about by different defective modules or a flawed citizen. For long haul applications, the shortfall of fitting recuperation components essentially will expand the likelihood of TMR disappointment event. TMR ought to be outfitted with a transient blunder recuperation procedure. The greater part of the past TMR-based mistake recuperation strategies proposed up to this point exploit retry components. These methods, be that as it may, are not reasonable for tight cutoff time applications, as the recompilation might bring about an undertaking consummation after its cutoff time. Retry based mistake recuperation components, continue onward recuperation systems are productive to be utilized in close cutoff time applications as no recompilation is required. Sc TMR utilizes a move onward approach and utilizes the sweep chain carried out in the circuits for testability purposes to recuperate the framework issue free state. Despite the fact that Sc TMR essentially diminishes the likelihood of TMR disappointments, it experiences two significant deficiencies. To begin with, Sc TMR can't recuperate a solitary flawed module in the TMR framework within the sight of idle shortcomings. A shortcoming is alluded to as idle on the off chance that it isn't engendered to the framework yields however purposes a bungle between the conditions of the TMR modules. Second, Sc TMR can't recuperate the framework on the off chance that numerous issues are at the same time appeared to the results of two modules.

#### 2. SMERTMR Framework

Filter chain based different blunder recuperation for TMR frameworks was proposed to address the weaknesses of Sc TMR. The proposed method can find and eliminate dormant issues in TMR modules as well as to recuperate the framework from various deficiencies influencing two TMR modules. Identification and recuperation are finished utilizing two methods of activities, examination and recuperation. In the correlation method of activity, the interior conditions of the modules are contrasted with track down the crisscross. One small step at a time correlation of the information is finished during examination and afterward the defective modules are found. In the recuperation method of activity, the information in the shortcoming free module is duplicated to the information in the flawed one.

#### A. State Chart

Typical method of activity shows the framework is doing its generally expected calculations and the sweep chains are impaired. Correlation mode is liable for the step by step examination of the information in the modules. This mode will figure out the defective modules toward the finish of examination activity. The data about the broken modules is then

ISSN No: 2583 -0368

## Scan Chain Dependent Approaching Technique towards Fault Recovery

passed to the recuperation mode, which starts the recuperation activity and reestablishes the framework states. Any disappointment during the activity will end with unrecoverable condition. Then all frameworks are stopped. At first the framework is in the typical method of activity. At the point when a blunder is recognized by the elector or when a designated spot signal is initiated, the framework changes to correlation method of activity. After correlation, in the event that no framework is found flawed, the control will go to the ordinary mode. In the event that it neglects to distinguish the shortcoming, it will go to the unrecoverable state. On the off chance that a couple of wrong modules are distinguished, the recuperation method of activity is finished. After effective recuperation, it will go to typical mode. Assuming it neglects to recuperate the framework the control passes to unrecoverable state. On the off chance that every one of the modules are defective, additionally the framework goes into the unrecoverable condition.

#### **B.** Comparison Mode

In this mode, the SMERTMR regulator empowers the output chains of the SMERTMR modules. The inner conditions of the modules are filtered out through the SCO pin of the sweep chain back-peddles. Every one of the pieces is contrasted utilizing XOR entryways associated with the results of each sets of modules. Toward the finish of correlation process, the flawed module is found.

#### C. Recovery Mode

In this mode, the SMERTMR regulator empowers the output chains of the SMERTMR modules. The SCI sign of shortcoming free modules is associated with the SCO sign of a similar module. Likewise, the SCI sign of the defective module is associated with the SCO of one of the shortcoming free modules. Hence the recuperation of the flawed module is finished.

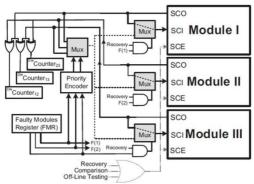

#### 3. Fault Location In SMERTMR

In the SMERTMR procedure, at whatever point the elector distinguishes a blunder, it enacts a mistake sign to alarm the SMERTMR regulator. Endless supply of the mistake signal, the SMERTMR regulator changes from the ordinary activity to the examination mode to find the defective modules. In the wake of finding the flawed modules, SMERTMR changes to the recuperation mode to recuperate the defective modules utilizing the condition of one of the shortcoming free modules. In this mode, the inside conditions of all TMR modules are moved out utilizing the sweep chains and all module matches (I/II, I/III, and II/III) are looked at. As displayed in Fig3.3, there are three counters, specifically, counter 12, counter13, and counter23, to store the quantity of mis-matches between every module matches. For instance, counter12 stores the quantity of jumbles between modules I and II. To this end, the SMERTMR regulator empowers examine chains of the SMERTMR modules and designs the multiplexers so that the SCO signal in every module is associated with the SCI sign of a similar module. During the shift activity, the inward conditions of the modules are thought about utilizing XOR doors.

At the point when a bungle is recognized, the comparing counter is increased by one unit. Utilizing this design, counter ij will contain the quantity of befuddles between modules I and j after Lsc clock cycles. The Shortcoming Finder Unit (Influenza) identifies the broken module utilizing the issue module location calculation. This season's virus stores the broken module number in the Flawed Modules Register (FMR). In the SMERTMR strategy, upon fruition of the examination mode, the shortcoming finder unit (Influenza) will decide the flawed modules. Calculation 1 diagrams how broken modules are recognized by This season's virus. As should be visible, on the off chance that all counters become zero, there is no defective module and subsequently the framework gets back to its generally expected mode. The condition proclamation in line 3 really takes a look at the presence of one flawed module. As examined before, on the off chance that there is just a single broken module, two out of three counters will have a similar non-no worth while the third counter will be equivalent to nothing. The condition articulation in line 6 really looks at the presence of two defective modules with no normal broken back-peddles. In the last two cases, the framework enters the recuperation mode to reestablish the right condition of the defective modules utilizing the condition of the shortcoming free modules. In the event that none of the past circumstances is substantial, the framework enters the unrecoverable condition. This season's virus stores the flawed module numbers in a register named the defective modules register (FMR). If FMR is equivalent to 110, it implies that modules I and II are broken. This data is utilized by the SMERTMR regulator during the recuperation mode. It is worth focusing on that in SMERTMR, rather than straightforwardly contrasting and casting a ballot the result of the three sweep chains, we first ensure that we have accurately recognized the shortcoming free module. Assuming one straightforwardly looks at and votes the results of the three sweep chains, it is conceivable that two out of three reproduction back-peddles are mistaken and an off-base state is composed back to each of the three modules. For this situation, the framework will keep on working in an off-base state. Such a condition isn't satisfactory in security basic applications.

#### A. Shortcoming Recuperation IN SMERTMR

In this mode, the SMERTMR regulator empowers the output chains of the SMERTMR modules and designs the multiplexers as follows: The SCI sign of shortcoming free modules is associated with the SCO sign of a similar module. Likewise, the SCI sign of the defective module is associated with the SCO of one of the shortcoming free modules., the

worth of the FMR register is utilized in the recuperation mode to choose the in-coming driver of the suitable sign driver for the SCI signals.

Fig3: SMERTMR in recuperation mode

Utilizing the setup 8, the condition of one of the shortcoming free modules is duplicated into the defective modules after Lsc clock cycles. While moving out the conditions of the modules in the recuperation mode, like the correlation mode, they are additionally com-pared to track down any jumble because of issues happening in the recuperation cycle. During the recuperation cycle, at whatever point a confound is distinguished and the relating counter worth containing the quantity of bungles is diminished by one unit. Toward the finish of the recuperation cycle, all counters ought to be zero. This is on the grounds that, for each jumble, the relating counter is increased by one unit during the examination cycle and is decremented by one unit during the recuperation interaction. If both of the counters is nonzero toward the finish of the recuperation interaction, it is demonstrative of one more shortcoming event during the recuperation cycle.

# 4. Reduced Issue Recuperation Strategy

High level blunder recuperation for the TMR frameworks, the proposed technique, is an improvement from every one of the current strategies. It tends to the impediments of the above depicted techniques. Hard ongoing frameworks frequently requires a shortcoming open minded framework which requires some investment for coming in to impact and recuperate the framework. Additionally in wellbeing basic applications like space applications, region and power utilization are significant imperatives. So the issue open minded framework ought to involve just least region and utilize less power. This multitude of necessities drove me to the requirement for a new and high level blunder recuperation method. I'm introducing an output chain-based move onward blunder recuperation strategy for TMR-based frameworks, which tends to the inadequacies of the multitude of existing techniques. The proposed strategy, called "High level blunder recuperation for TMR frameworks", can find and eliminate dormant shortcomings in TMR modules as well as to recuperate the framework from numerous flaws influencing two TMR modules. The fundamental thought is to reuse the accessible output chains dedicated for testability purposes to analyze the interior territories of TMR modules to find and reestablish the right condition of defective modules utilizing the condition of non-broken modules. The proposed framework can identify the blunder that happens in a triple measured excess framework and to recuperate a similar utilizing least hardware and less time. The framework additionally means to manage the state of numerous deficiencies showing up at different modules. The framework is really a TMR framework with an extra regulator. The regulator is the cerebrum of the framework. It is liable for both mistake discovery and recuperation. This thusly lessens the time and region required. Examination and recuperation tasks are finished simultaneously. After examination of each piece, the crisscrossed pieces are revamped simultaneously. In the wake of contrasting each piece, the right piece is composed into a cradle, and the cushion yield is thusly composed into the module. This circuit is for the recuperation activity of the modules. We can likewise incorporate the counters and the Issue Finder modules from the SMERTMR, so the broken modules can be identified. Yet, progressively frameworks we know nothing about the activities that are going inside the modules and we really want a programmed recuperation.

# **5. Reduced-Accuracy Overt Repetitiveness**

RPR is an overt repetitiveness strategy like TMR that requires less equipment above by utilizing diminished accuracy (RP) number-crunching in two of its three copies. It exploits the way that RP Math can be a decent gauge of calculations that utilization higher accuracy. While TMR safeguards the whole circuit and gives a blunder free result, RPR just restricts the mistake at the result of a module. RPR enjoys an upper hand over TMR when it can adequately restrict the size of the SEU-initiated commotion at a lower equipment cost.RPR isn't fit to safeguard any kind of hardware as TMR is. Activities that can be approximated with less equipment than the standard module are contender for RPR. RPR has, for the most part, been utilized to safeguard number juggling operations. In expansion the estimation and the choice equipment expected to pick the last result should not surpass the expense of TMR, in any case, any benefit of RPR is lost.

#### A. Implementation

The RPR strategy utilizes n-digit limited drive Reaction (FIR) channel (a channel with n-cycle registers and coefficients) safeguarded with RPR. The figure shows that the contributions to the channel are sets of three, similarly as with TMR, and that the second and third imitations of the circuit are executed with RP (k-piece, where k < n)FIR channels.

## Scan Chain Dependent Approaching Technique towards Fault Recovery

Note that the choice blocks and results can be sets of three too to keep away from weak links in those modules. The results of the three indistinguishable choice blocks are casted a ballot.

#### 6. Results and Conversation

#### A. Result of SMERTMR

In the correlation mode, the inward conditions of all TMR modules are moved out utilizing the sweep chains and all module matches (I/II, I/III, and II/III) are looked at. There are three counters, to be specific, counter12, counter13, and counter23, to store the quantity of confuses between every module matches. For instance, counter12 stores the quantity of bungles between modules I and II. To this end, the SMERTMR regulator empowers check chains of the SMERTMR modules and designs the multiplexers so that the SCO signal in every module is associated with the SCI sign of a similar module. During the shift activity, the inward conditions of the modules are thought about utilizing XOR doors. Whenever a jumble is identified, the relating counter is increased by one unit. While moving out the conditions of the modules in the recuperation mode, like the examination mode, they are additionally com-pared to track down any confuse because of deficiencies happening in the recuperation cycle. During the recuperation cycle, at whatever point a crisscross is distinguished and the relating counter worth containing the quantity of confuses is diminished by one unit. Toward the finish of the recuperation interaction, all counters ought to be zero. This is on the grounds that, for each jumble, the relating counter is increased by one unit during the correlation cycle and is decremented by one unit during the recuperation interaction. If both of the counters is nonzero toward the finish of the recuperation interaction, it is demonstrative of one more shortcoming event during the recuperation cycle. On the off chance that the framework enters the unrecoverable condition it will ends.

Fig 2: Result of Sc TMR

# 7. Conclusion

The framework is intended for the identification and recuperation of different blunders in TMR based frameworks for wellbeing basic applications. It reuses the output chain back-peddles for the course of mistake identification and recuperation. Here the continue onward mistake recuperation method is utilized in which the condition of the shortcoming free module is duplicated in to the flawed one. This strategy recognizes, finds, and amends various shortcomings influencing single and two defective modules. The plan is created and arranged to VHDL net rundown .Here we look at the current technique ScTMR and our proposed strategy SMERTMR with XILINX ISE 13.2

#### **References**

- 1. P.K.Samudrala, J.Ramos, and S.Katkoori, (2004) "Selective triple modularred undancy(STMR)based single-eventupset(SEU) to lerant synthes is for FPGAs, "IEEE Trans. Nucl. Sci., vol. 51, no. 5, pp. 2957–2969

- 2. S.D'Angelo, C.Metra, and G.Sechi, (1999) "Transient and permanent fault diagnos is for FPGA-based TMR systems," in Proc. Int. Symp. Defect

- 3. Fault Tolerance VLSISyst,pp. 330–338.

- 4. Omar Hiari, Waseem Sadeh, and Osamah Rawashdeh(2012), "Towards Single Chip Diversity TMR for Automotive Applications," Volume: 43, Issue:6,Page(s):2742–2750.

- 5. J.A.Abraham and D.P.Siewiorek,(1974) "An algorithm for the accurate reliability evaluation of triple modular redundancy networks," IEEE Trans.

- 6. Comput., vol. 23, no. 7, pp. 682-692

- 7. I. Koren and S. Y. H. Su(1979), "Reliability analysis of N-modular redundancy systems with intermittent and permanent faults," IEEE Trans. Comput., vol. 28, no. 7, pp. 514–520, Jul.

- 8. M.Zhang,S.Mitra,T.M.Mak,N.Seifert,N.J.Wang,Q.Shi,K.S.Kim,N.R.Shanbhag,andS.J.Patel,(2006) "Sequentialele mentdesign with built-insofterror resilience," IEEE Trans. Very Large Scale Integr.(VLSI)Syst.,vol.14,no.12,pp.1368–1378

- 9. F.L.Kastensmidt,L.Sterpone,L.Carro,andM.S.Reorda.,(2005) "OntheoptimaldesignoftriplemodularredundancylogicforSRAM-basedFPGAs," in Proc. Design Autom. TestEur. Conf. Exhibit, pp. 1530–159

- 10. FirozAhmedSiddiqui,PuranGur(2014) "Scan-Chain-BasedMultipleErrorRecoveryinTMRSystems(SMERTMR):AReview" ISSN:2349-4689Volume-02