September-October 2023, Volume 3(05), 10-13.

# **An Innovative Approach to the Diagnosis of Inconsistencies Caused At Numerous Locations**

# Noorul Ameen<sup>1</sup>, George Thomas<sup>2</sup>, John Jacob<sup>3</sup>

1.2.3 Asst. Prof. Department of Electronics and Communication Engineering, KMCT College if Engineering, Kerala, India.

Article Type: Research

OPENACCESS

Article Citation:

Noorul Ameen<sup>1</sup>, George Thomas<sup>2</sup>,

John Jacob<sup>3</sup> "An Innovative

Approach to the Diagnosis of

Inconsistencies Caused At

Numerous Locations"," International

Journal Of Recent Trends In

Multidisciplinary Research", SeptemberOctobe 2023, Volume 3(05), 10-13.

©2027 The Author(s). This is an open access article distribute dunder the terms of the Creative Commons Attribution (Leene, which permits unrestricteduse, distribution, and peroduction in any medium, provided the original author and source are credited. Published by 5th Dimension Research Publication.

**Abstract:** Testing is a significant early move toward plan of VLSI. With a huge number of semiconductors being coordinated in one chip, various flaws might exist. To precisely and proficiently recognize the shortcoming areas, a solid shape based EPP examination procedure is proposed. The determined rate addresses the EPP of the infused shortcoming. In the circuit, the 3D square upsides of area at the underlying stages are changed and the blunder count is determined. This is finished until the blunder count decreases to nothing. Both the methods are applied to ISCAS '89 benchmark circuits and the boundaries, for example, region, speed and power are registered. It tends to be seen that the region and power are decreased astoundingly by EPP strategy contrasted with FEG technique and the speed increments around by multiple times. The outcomes show that the EPP technique is more beneficial than the diagram based approach.

**Key Word:** adaptation to internal failure, unwavering quality, like lihood based, numerous issue finding.

# 1. Introduction

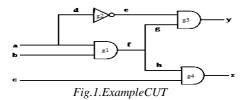

In the development of coordinated circuits, testing is finished to distinguish imperfect chips. Testing is likewise finished to analyze the justification behind a chip disappointment to further develop the assembling system. Testing a computerized circuit includes applying a proper arrangement of information examples to the circuit and checking for the right results. In any case, worked in individual test (BIST) procedures have been created in which a portion of the analyzer capabilities are consolidated on the chip empowering the chip to test itself. BIST gives various notable benefits. It dispenses with the requirement for costly analyzers. It gives quick area of bombed units in a framework in light of the fact that the chips can test themselves simultaneously. The rising pin count, working rate, and intricacy of IC's is surpassing the capacities of outside analyzers. BIST gives answers for these issues. Fig. 1. is a block graph showing the engineering for BIST. The circuit that is being tried is known as the circuit-under-test (CUT). There is a test design generator which applies test examples to the CUT and a result reaction analyzer which really looks at the results. The test design generator should create a bunch of test designs that gives high shortcoming inclusion to completely test the CUT.Pseudo-irregular testing is an alluring methodology for BIST. A straight criticism shift register (LFSR) can be utilized to apply pseudo-irregular examples to the CUT. A LFSR has a straightforward design requiring little region above. In addition, a LFSR can likewise be utilized as a result reaction analyzer in this way filling a double need.

# 2. Background Work

In [1], a viable numerous imperfection conclusion procedure that doesn't rely upon bombing design attributes. The system comprises of a moderate deformity site recognizable proof and end calculation, and an imaginative way based imperfection site disposal method. In any case, it tends to be utilized exclusively for Single Area At an At once of issues. A finding of interconnect opens was proposed in [2] which considers any conceivable open area along the blemished line utilizing the full open portion (FOS) model. Be that as it may, open blames in any event, when analyzed, are not exact. In [3], a Support design which is a weak example which can be made sense of by a solitary area shortcoming. Brace designs are utilized to develop a composite image of the different flaws utilizing the least defective areas. However, on extending them to analyze defer issues, the suspicion that the shortcoming reenactment results match postpone deformity conduct in genuine silicon becomes ridiculous. Two shortcoming analysis strategies for further developing various shortcoming finding goal are proposed in [4]. This is insufficient as it has above in region and postponement. In [5], a chart based approach is utilized in which Shortcoming Component Diagram (FEG) is developed to analyze the deficiencies. This strategy, in spite of the fact that it distinguishes various shortcoming areas, is with less exactness.

ISSN No: 2583 -0368

# 3. EPP BASED APPROACH

To precisely and effectively assess the mistake spread likelihood, we propose a 3D square based EPP investigation method. Rate addresses the EPP of the infused shortcoming. Monte Carlo reenactment is profoundly precise yet exceptionally tedious on the grounds that it needs to take care of the entire info set for each shortcoming to get an EPP. Accordingly, existing Monte Carlo recreation strategies need to compromise exactness against computational intricacy interestingly; static investigation utilizes the likelihood hypothesis to register EPPs. Fig. 2. gives a guide to an instance of utilizing 3D shapes and covers. For model, to find the 3D squares that have a result esteem 0 under the two the AND rationale and the OR rationale, a point of interaction computation on cover 0 of the AND rationale and cover 0 of the OR rationale is given as follows:On the other hand, the append of two 3D squares, meant as a V b, is the association of two 3D shapes a, b. Accepting the transmission likelihood of each info wire is same, the strategy proposed can utilize primary data to rapidly assess signal probabilities of inner wires that interconnect LUTs. A while later, EPPs are processed by involving signal probabilities for off way wires and by utilizing blunder spread rules for on way wires. With the assistance of likelihood hypothesis, static investigation just has to cross the whole circuit only two times to get EPPs for all deficiencies, so its computational intricacy is extremely low.

#### A. Computation Of EPP

EPP is computed by tracing the paths in the circuit and assigning probabilities to the paths based on the number of gates present in the path. This could be easily explained by using the CUT in the Fig. 3.

The truth table of the given example circuit is given in Fig.2.

| Inputs |   |   | Outputs |   |

|--------|---|---|---------|---|

| a      | b | С | y       | Z |

| 0      | 0 | 0 | 0       | 0 |

| 0      | 0 | 1 | 0       | 0 |

| 0      | 1 | 0 | 0       | 0 |

| 0      | 1 | 1 | 0       | 0 |

| 1      | 0 | 0 | 0       | 0 |

| 1      | 0 | 1 | 0       | 0 |

| 1      | 1 | 0 | 0       | 0 |

| 1      | 1 | 1 | 0       | 1 |

Fig.2. Truth table for fault-free CUT

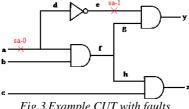

Introducing the faults allocations a and e with SA-0andSA-1respectivelyas shown in Fig.3.

Fig.3.Example CUT with faults

A comparator is used to compare between the faulty and fault-free values and can be identified. By exercising the input patterns, the failure patterns are found to be p1=110 and p2=1110. This could be given by the truth table in Fig. 4. This is noted for the first step alone and stored, so that it can be utilized for the steps until the entire computation is over. Even though, there are variationsate a chstage's output, the initial table is used for comparison.

The paths in the circuit correspond to the propagation from the primary input to the primary output. There are six paths existing in the example CUT, and it can be given as follows:

| Inputs |   |   | Outputs |   |

|--------|---|---|---------|---|

| a      | b | С | y       | Z |

| 0      | 0 | 0 | 0       | 0 |

| 0      | 0 | 1 | 0       | 0 |

| 0      | 1 | 0 | 0       | 0 |

| 0      | 1 | 1 | 0       | 0 |

| 1      | 0 | 0 | 0       | 0 |

| 1      | 0 | 1 | 0       | 0 |

| 1      | 1 | 0 | 1       | 0 |

| 1      | 1 | 1 | 1       | 1 |

Fig. 4.Truthtablefor faulty CUT

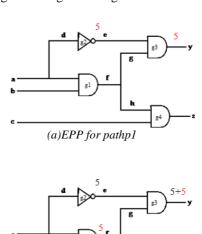

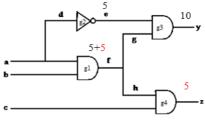

Using these paths the EPP computation is done. Considering path p1, the number of gates encountered in the path is 2, hence, the probability is equally divided as 5and5 (taking total probability as 10, for easier calculation).

The value is equally divided among the gates En countere din the path If there are two gates it is divided in to(10/2=5) for a chgate. If there are three gates, each gateh as (10/3=3.33) distributed equally and soon.

Considering each path, the EPP assignment is given in Fig. 5.

(b)EPP for pathp2

(c)EPP for pathp3

### 1. Simulation

# A. Schematic Of CLB Based Adder

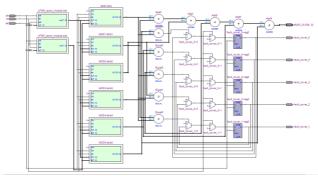

The methods are tested using a CLB based adder. The CLB blocks are made up of AND, OR and EX-OR gates. It consists of numerous elements which are named as CLB\_(gate type)\_(gate number). Faults are injected at certain locations randomly and both the procedures are applied via coding. Once applied, the results can thus be tabulated and compared.

Fig.10.shows the schematic of the CLB based adder used for testing. Its simulation results are specified below.

Fig.6.Schematic of CLB Based Adder

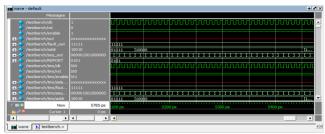

The output produced by the graph-based technique is given in Fig. 7.

Fig.7.Output of Graph Based method

The error count need to be calculated at each step and can be related to the EPP percentage. If the path has 10 gates, the probability is assigned as 1 each and the gate which holds a number of values are summed up and given as a whole value. This leads to a huge value at the gate which is associated with more number of gates. The error count in the output is giveninFig.07

# 4. Conclusion

The different issues were identified utilizing other existing procedures and the outcomes were thought about. Later on, another single cycle access test structure for rationale test. It will takes out the pointless unique power utilization issue of ordinary shift-based check chains during exchanging progress in the sweep FF and furthermore decreases the getting to time into one clock cycles. This prompts more practical circuit conduct during stuck-at and at-speed tests. It empowers the total test to run at a lot higher frequencies equivalent or near the one in useful mode. In this work intricacy will be expanded straightly with configuration level. To hold the plan intricacy by gathering the plan units as a different free pages and getting to will be done by choosing pages.

# **References**

- 1. Rodríguez- Montañés. R, Arumí, D, Figueras S. Einchenberger, Hora. C, Kruseman .B(2010), "Diagnos is of Full Open Defects in Inter connect Lines with Fan-out", IEEE, pp. 233-238.

- 2. Yung-Chieh Linand Kwang-Ting Cheng(2006), "Multiple-Fault Diagnos is Based on Single-Fault Activation and Single-Output Observation", EDAA.

- 3. Yung-ChiehL in, Feng Luand Kwang-Ting Cheng(2007), "Multiple-Fault Diagnos is Based On Adaptive Diagnostic Test Pattern Generation", IEEE Transactions.

- 4. Jing Ye, YuHu, XiaoweiLi, Wu-Tung Cheng, YuHuang and Huaxing Tang (2014), "Diagnose Failures Caused by Multiple Locations at a Time", IEEE Transactions.